에피텍시

: 순도 높은 초순수 실리콘 웨이퍼를 시드(기판)로 삼아 그 위에 ~10um의 극초순수 실리콘 웨이퍼를 형성하는 방식.

기판이 시드층으로 사용되기 위해서는 격자 구성이 결정질(단결정)이어야 한다.

○ 시드층이 결정질(단결정)이어야 하는 이유

: 시드층에 극초순수 웨이퍼를 형성(에피 공정)하는 이유는 결함 없는 막을 마련해 전자 캐리어들을 손쉽게 이동시키기 위해서이다.

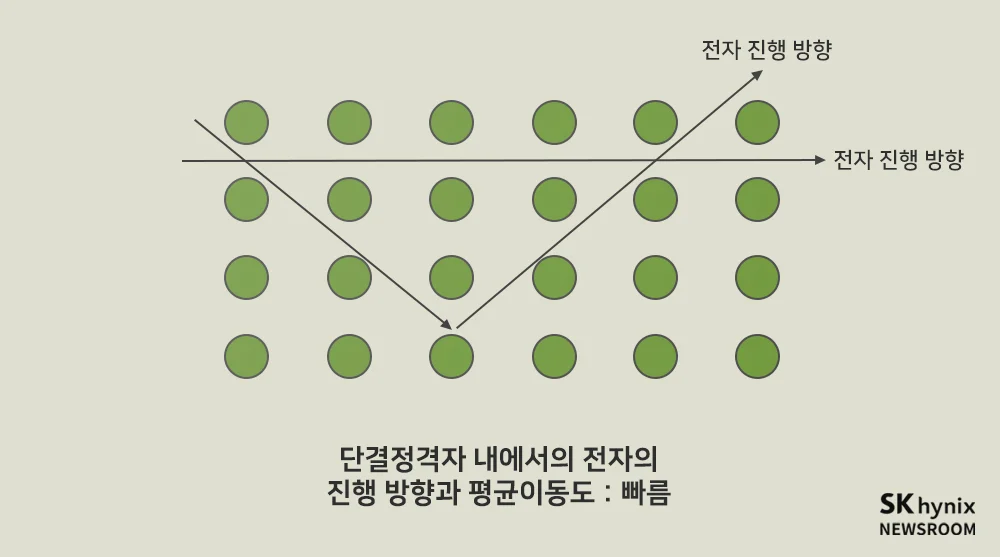

단결정의 경우 전자끼리 부딪힐 확률이 낮아져, 전자의 평균 이동 거리인 평균자유행로(MFP)가 길어지므로 전자의 이동도 또한 크다.

반면 단결정이나 비정질 격자 배열은 전자 캐리어의 이동도를 약화시키고 전자 트랩을 쉽게 발생시킨다. (비정질 중 화합물 반도체는 예외)

○ 격자상수의 영향

: 격자상수란 실리콘 원자와 원자 사이 공유결합을 이루고 있는 거리.

격자상수는 캐리어의 이동도와 위아래층의 열팽창계수에도 영향을 끼치므로 기판층과 시드층의 격자상수가 같은 것이 좋다. (D1 = D2)

○ 호모 - 에피텍시: 시드층과 에피층의 결정 구조 간격이 일치하는 경우. (실리콘 - 에피텍셜 층)

○ 헤테로 - 에피텍시: 시드층의 결정 구조 간격이 에피층의 결정 구조 간격보다 크거나 작은 경우. (실리콘 - 절연막)

'반도체 2모저모' 카테고리의 다른 글

| High - K와 HKMG (0) | 2024.04.15 |

|---|---|

| 산화 공정 순서 & 여러 가지 요인들 (0) | 2024.04.15 |

| 산화 공정 (2) | 2024.03.29 |

| 산화 공정 - 절연막 (2) | 2024.03.29 |

| CMOS (2) | 2024.03.29 |