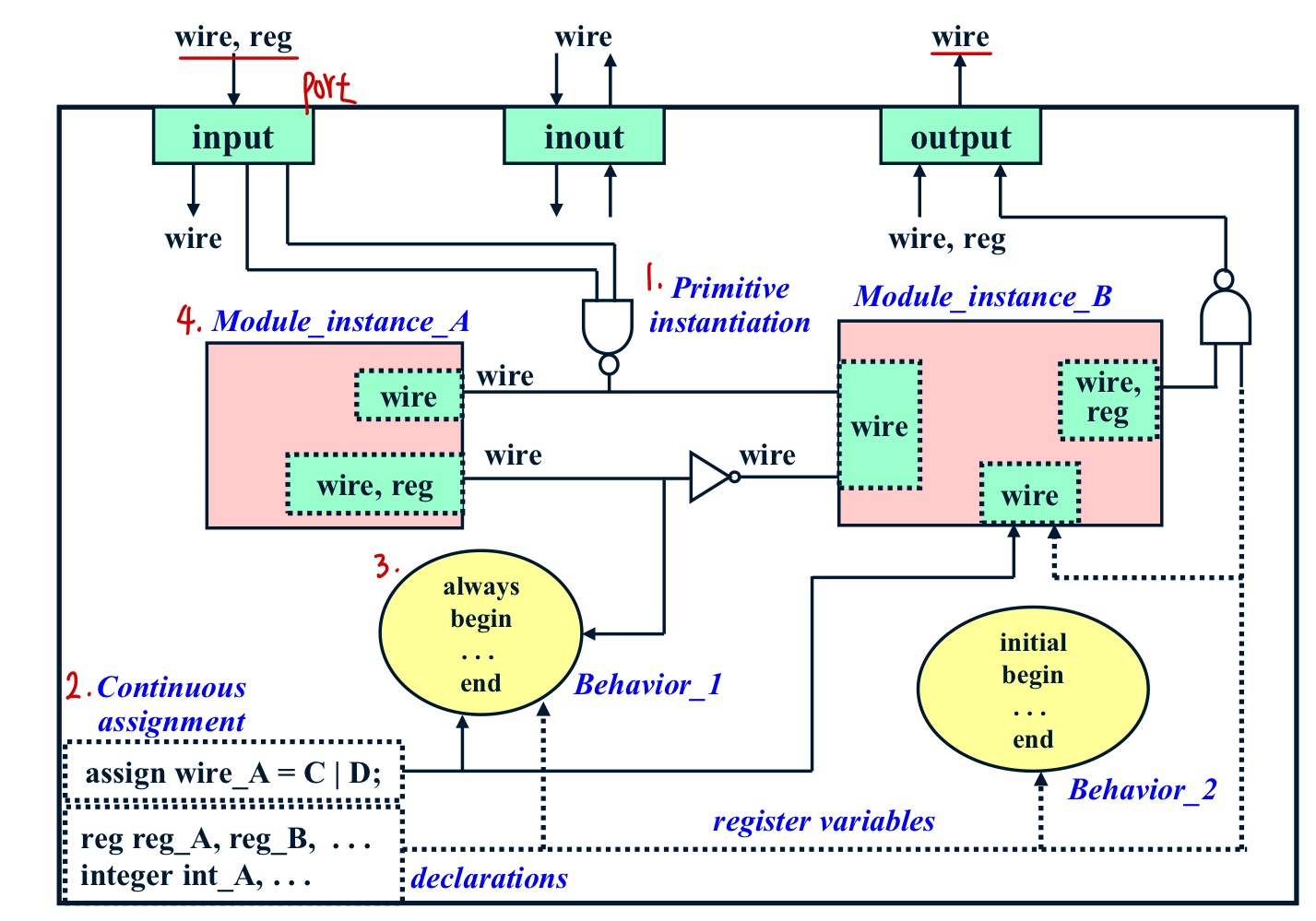

Verilog HDL module

Verilog 어휘 규칙

수 표현

✅ 정수형(integer)

- 형식: <size>'<base><value>

size: bit 크기(기본값: 32 bit unsigned)

': bit

base: 밑수(진법)를 지정하는 문자(d, D: 10진수, h, H: 16진수, o, O: 8진수, b, :B 2진수)

value: 값

ex) 8'b10101010 // 8비트 2진수 (170)

✅ 부호

1) unsigned 상수(부호 없는 정수)

: Verilog의 기본 숫자 상수는 unsigned(부호 없음)으로 해석, 음수를 표현할 수 없다.

2) signed 상수 (부호 있는 정수)

: signed 변수를 선언하면 2의 보수 방식으로 음수를 표현할 수 있다.

base에 s를 붙여서 선언 가능

ex) 8'sb10101010 // 8비트 부호 있는 2진수 (-86)

※ 2의 보수: MSB가 1이면 음수, 0이면 양수

비트 반전 후 1을 더하는 방식

ex) 1001 → 0110 +1 = 0111(-7)

키워드

: Verilog 구성 요소를 정의하기 위해 미리 정의된 식별자

'디지털회로 2모저모' 카테고리의 다른 글

| Data Type and Operators (0) | 2025.02.13 |

|---|---|

| Verilog HDL 개요 (0) | 2025.02.12 |